包含Smart Zynq (SP 版)的原理图,注意事项,以及后续更新的转接板的原理图等一些资料

首先感谢各位的关注和支持,有任何问题可以直接在本站留言,或者在淘宝搜索店铺:杭海电子科技 。

另外备注 本页是 SP 版本的 资料,如果是Smart ZYNQ 标准版 或者SP2版 SL版 的主板 请看对应的内容 (SP2 和SP版的区别在于 屏幕不同SP2是1.3寸240×240屏,SP是1.47寸172*320屏,其他完全一致)

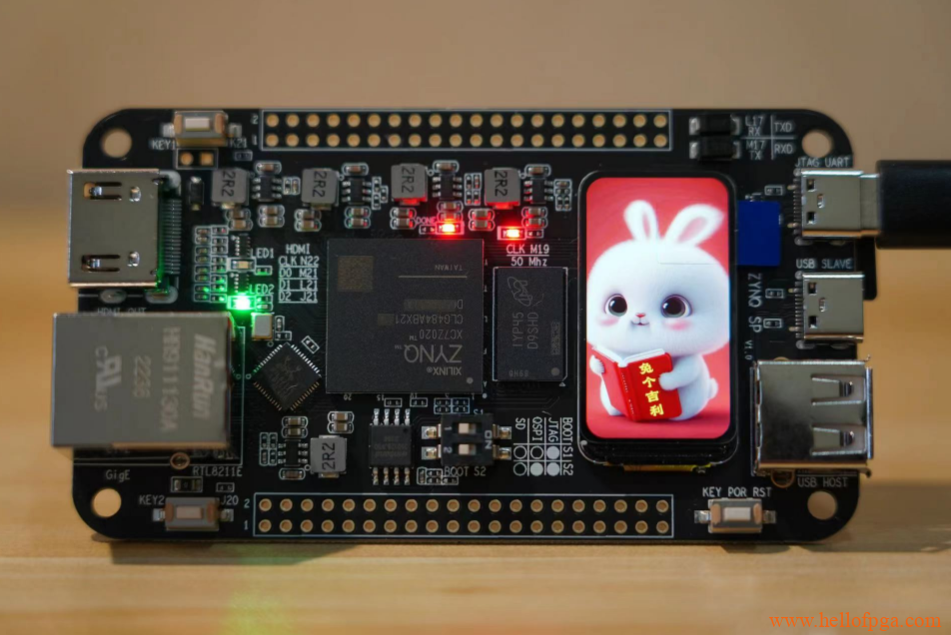

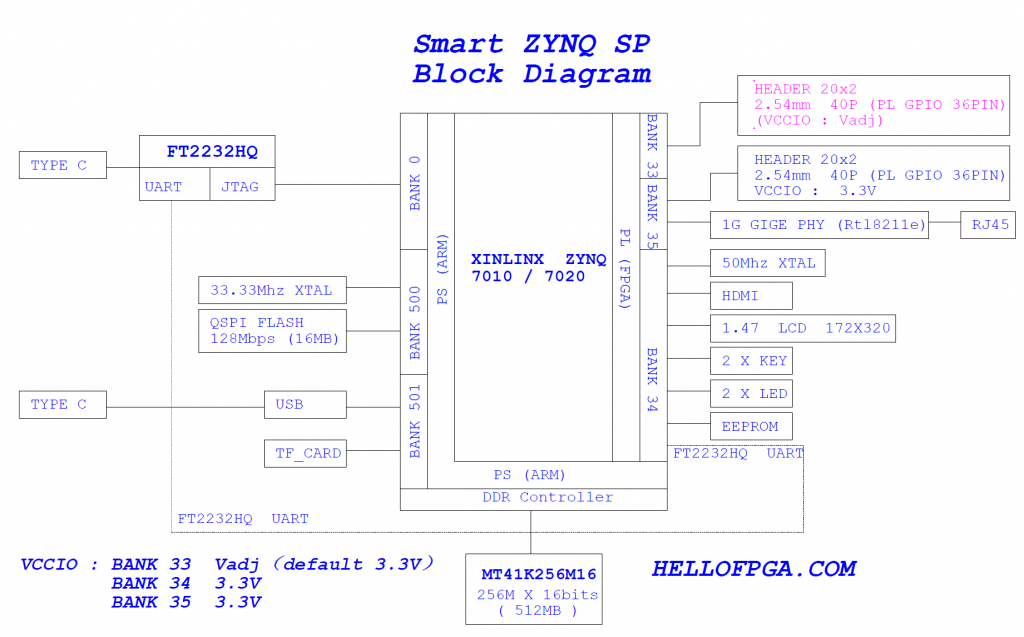

Smart ZYNQ SP 主板资源

- 主芯片:ZYNQ XC7Z020-CLG484

- 主板层数:8层(沉金工艺)

- DDR内存 : 256M x 16bit (512MB)

- FLASH : 128Mbits (16MB)(接PS端用于系统启动)

- EEPROM: 24C02 2kbits

- TF插槽:microSD 插槽 (TF卡插槽,可用于系统启动)

- 时钟 : PS端:33.33M有源晶振 , PL端:50M有源晶振

- 网络: 一路千兆以太网RTL8211E (接PL端,PS也可使用)

- HDMI: 一路HDMI 接口(IO模拟)

- JTAG: 板子集成了 xilinx jtag 下载器部分功能(板载)

- USB: 板子自带USB2.0 PHY,可作USB HOST,或USB SLAVE

- 串口: 带一路USB-UART(连接至PL端,PS端也可使用

- 按键: 2个按键(PL端) + 1个POR硬件复位按键

- LED: 2个可编程LED(PL端 )+Done 指示LED + 电源指示LED

- LCD: SP2主板带一个1.47寸的 SPI LCD屏 320×172(接PL端,PS也可使用)

- 拨码开关:双路拨码开关(负责启动方式选择)

- 逻辑IO: 总共引出68个FPGA_IO,所有引出的管脚均以差分线方式两两引出(差分线内等长)(全都由PL端引出,PS可通过EMIO方式映射)

- 引出的GPIO中 其中一边的bank电压单独可调(通过调整一个0805封装电阻)

- 电源:主板可以通过TYPE C口(JTAG或 USB SLAVE)进行供电,或者用转接板通过排针给主板的VCC脚供上5V电源

SP 和SL 版 相同资源的程序 是可以完全兼容的,管脚和GPIO的线序也完全一致,除USB HOST ,USB SLAVE 以及 板载 LCD 等SL版没有的功能外 其余资料相通

主板原理图如下:(最新更新 2023年5月1日)

尺寸图

板子上排针的 引脚长度报告:(备注 差分线 组内都做了等长,组外没有做等长,如果设计底板过程中对等长有要求,请参考下列长度报告)

板子上所有功能IC 的数据手册:

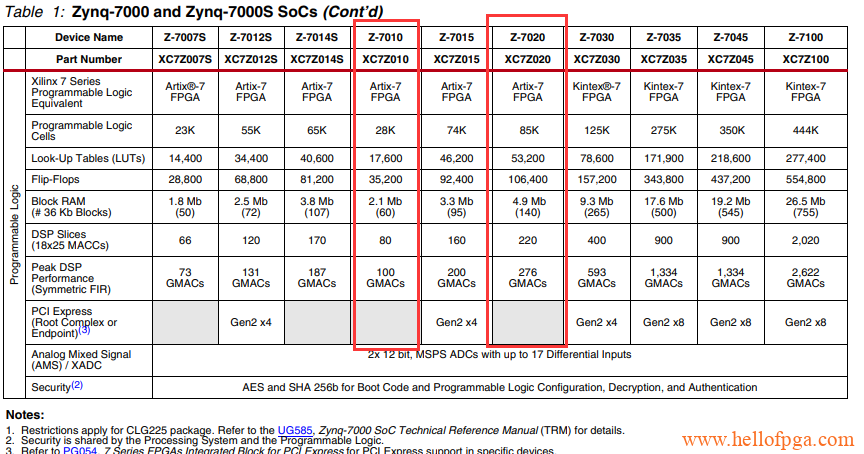

7010 和7020的PL资源 如下图所示

注意事项

- 关于BANK33的电压, BANK 33电压可以通过调整背面两颗0805大小的电阻(板子上丝印标注为RA RB)来实现电压的调整(出厂默认是3.3V)

- Smart ZYNQ SP2板子上的USB SLAVE 和 USB HOST 是共用ZYNQ的USB资源的,所以同一时间只能使用一种功能(USB HOST 和USB SLAVE 不可同时外接设备,另当USB 功能作为HOST使用时如需要用USB SLAVE口为板子进行供电请接USB适配器而不是接电脑)。

- 板子上的两个TYPE C接口都可为板子进行供电,板子排针上的VCC口也可以外接5V 为板子进行供电,USB和排针外接供电互不冲突(USB有二极管作电源防倒流保护),另外备注:部分台式机前面的USB口线损较大,如用台式机的USB供电出现不稳定的情况,请尝试连接台式机背后的USB口。

- 部分笔记本和电脑的USB口输出电流限制在5V 500ma,这对于主板的运行已经足够了, 但如果主板需要外接模块,或者USB口外接功率较大的USB设备导致工作不稳定时,可以通过排针或者外接转接板单独为板子提供5V电源(排针的VCC脚)。另外外接USB设备或者模块时,建议先在断电情况下接好设备或模块,再对主板进行上电。

- 排针上的VCC口可作为电源输入,也可作为电源输出。作为输入时:可外接5V电源(即通过转接板,或者底板为板子供电,如用杜邦线供电效果会差一些)。作为输出时:(没有外接5V电源,仅通过USB供电时)可以输出4.5-4.7V的电压(即主板为转接板供电)。

- 板子上的 POR RST 是整个硬件的复位按钮 (优先级高于任何程序,只要此按键按下整个系统将根据BOOT启动方式重新启动)。

随板预下载的演示程序介绍 (boot模式选择 QSPI FLASH再上电)

- HDMI输出720p的 测试彩色条纹

- 1.4寸屏幕输出测试彩色条纹

- UART以一秒钟为间隔发送 “hello world”

- LED灯在上电后以流水灯的方式 来回点亮 (一旦按下KEY1 KEY2 任意按键,则流水灯停止,程序切换到对应按键方向的灯亮起)

- USB slave 接口用数据线和电脑连接 可以看到一个ram 映射的255MB的 虚拟U盘(因为是RAM映射的,所以断电数据会丢失,请不要存放重要数据,仅供测试)

可供测试的 TF固件

(使用方法:将文件下载并解压缩,将内容复制到FAT32格式的TF卡的根目录,并插入到主板上,拨码开关设置成SD启动,并按下板子上的POR复位键盘)

1.全功能测试

- 所有的GPIO (排针输出端)进行流水灯闪烁

- HDMI输出720p的 测试彩色条纹

- 1.4寸屏幕输出彩色图片

- UART以一秒钟为间隔发送 “hello world”

- LED灯在上电后以流水灯的方式 来回点亮 (一旦按下KEY1 KEY2 任意按键,则流水灯停止,程序切换到对应按键方向的灯亮起)

- USB slave 接口用数据线和电脑连接 可以看到一个ram 映射的255MB的 虚拟U盘(因为是RAM映射的,所以断电数据会丢失,请不要存放重要数据,仅供测试)

2. 网络和USB HOST测试固件(linux 进入账号root 密码 root)

- 用串口通过命令行登录Linux, 然后插上网线连接路由器,通过ping来测试网络功能

- 插入FAT32格式的U盘,用命令行相关命令来访问U盘 (SL版不带此功能)

- 操作上可以参考 下面两个工程最下方演示的操作 ZYNQ linux开发 章节八 Petalinux 千兆以太网络功能的测试( Smart ZYNQ SP&SL 版) 以及工程 Smart ZYNQ(SP) 工程二十七 基于PS的 USB slave功能测试(即ZYNQ模拟U盘的功能测试)

已整理的一些图文例程(持续更新中)

备注 本站所有的资料都是基于VIVADO2018.3版本的,如果不熟悉开发过程,版本尽量保持一致

关于主板

- 关于7020芯片磨码的说明

- Smart Zynq SP 亚克力保护板图纸(非Smart ZYNQ SP2或标准版)

- ADB_ZD02-正点原子模块转接板(可连接摄像头及AD、DA等模块)附gerber文件可以直接打板

基于Smart ZYNQ (SP SP2 SL) 的FPGA实验

- 当遇到ZYNQ ,SDK debug失败报错的解决方法

- ZYNQ板PL部分程序添加复位信号的几种办法

- Vivado 2018.3 下载及安装

- Verilog 快速上手笔记

- Vivado 2019.2 以上带 vitis 版本的简单教程演示 (本文大多数例子都是基于2018.3创建的,所以本章节选看)

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验一 用ZYNQ的PL资源点亮一个LED (完整图文)

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验二 用ZYNQ的PL(FPGA)设计流水灯

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验三 PL部分按键功能演示(IO输入功能)

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验四 Vivado自带的仿真功能演示

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验五 FPGA 硬件调试 ILA功能的演示

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验六 FPGA的 VIO在线调试功能测试

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验七 FPGA资源的PWM演示

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验八 FPGA片内资源MMCM/PLL 时钟模块的测试

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验九 FPGA片内资源 BLOCK RAM IP核的使用

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验十 在PL端调用片内XADC资源来读取 ADC对应管脚的电平电压

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验十一 基于双路高速ADC模块的信号采集实验

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验十二 基于ZYNQ PL资源的HDMI功能演示

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验十三 基于PL的RGB888屏幕调试 ( 5INCH 800X480屏)

- 基于Smart ZYNQ(SP/SP2/SL 版) 的FPGA实验十四 基于PL端的 FPGA UART串口通讯实验

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验十七 基于FPGA的千兆以太网UDP环回实验

- 纯FPGA程序固化啊部分可以参看PS的实验:

- PS端为PL端提供时钟部分可以参看PS的试验:

- PL端与PS端交互的部分可以参看下面三个PS实验:

基于Smart ZYNQ (SP SP2 SL) 的PS实验

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验一 GPIO之用EMIO方式点亮LED(完整图文)

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验二 GPIO之用AXI-GPIO方式点亮LED (完整图文)

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验三 GPIO之按键功能演示(EMIO方式)

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验四 外部中断实验

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验五 定时器中断实验

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验六 将程序固化至QSPI FLASH(FLASH启动)

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验六 (补充) 纯FPGA程序 固化至QSPI FLASH

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验七 将程序放置在TF卡并进行TF卡启动演示

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验八 UART功能演示

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验九 QSPI FLASH读写测试

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验十 千兆网络初测(基于EMIO)

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验十一 USB slave功能测试(即ZYNQ模拟U盘的功能测试)

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验十二 ZYNQ PS 端的双核AMP实验

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验十三 PS与PL数据交互之 PS访问 PL端的reg 寄存器

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验十四 PS与PL数据交互之 PL(FPGA)读写 PS端DDR的实验

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验十五 PS与PL数据交互之 PS访问 PL端的BRAM资源实现PS与PL数据交互

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验十六 通过PS部分来为PL逻辑提供时钟(做工程时的常用方法)

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验十七 调用片内XADC资源 来实时读取芯片的电源和温度等信息

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验十九 用VDMA模块来缓存图像并在HDMI上显示(一)PS端彩条纹的显示

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验二十 用VDMA模块来缓存图像并在HDMI上显示(二)显示TF卡上的BMP格式图片

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验二十一 5寸RGB屏实验:用VDMA模块来缓存图像并在LCD上显示(一)PS端彩条纹的显示

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验二十二 5寸RGB屏实验: 用VDMA模块来缓存图像并在LCD上显示(二)显示TF卡上的BMP格式图片

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验二十三 5寸RGB屏实验: 电容触摸部分DEMO

十月之后开始对原先的基础工程进行再次整理,上述是整理后的工程,原先未整理的工程在下方:

Smart ZYNQ(SP版) 工程二十六 用zynq的PS的硬件SPI资源驱动彩色LCD (SL版不带此功能)

基于Smart ZYNQ (SP SP2 SL) 的LVGL实验

基于本站 ZYNQ 主板的 LVGL(V8.3.10版本)的手把手移植教程(VDMA+DMA方式)

基于Smart Zynq 的Petalinux部分图文教程

- Petalinux开发准备工作:

- 基于Smart Zynq 的Petalinux开发:

- 基于Smart Zynq 的Petalinux开发 章节一 Vivado 基础硬件工程搭建

- 基于Smart Zynq 的Petalinux开发 章节二 在 Ubuntu 上完成 Petalinux 的工程创建及编译全过程(TF卡启动)

- 基于Smart Zynq 的Petalinux开发 章节三 创建可用于Petalinux 系统启动的SD卡(包含boot和rootfs分区)

- 基于Smart Zynq 的Petalinux开发 章节四 启动验证

- 基于Smart Zynq 的Petalinux开发 章节五 通过SSH远程登录petalinux系统

- 基于Smart Zynq 的Petalinux开发 章节六 Windows 通过 SCP 命令 远程传输文件给petalinux 系统

- 基于Smart Zynq 的Petalinux开发 章节七 GPIO的输入输出实验

- 基于Smart Zynq 的Petalinux开发 章节八 GPIO的输入输出实验二——通过编写应用程序来控制

- 基于Smart Zynq 的Petalinux开发 章节九 USB HOST实验

- 基于Smart Zynq 的Petalinux开发 章节十 从QSPI FLASH 启动LINUX镜像

- ZYNQ linux开发 章节十 Petalinux 板载LCD 显示linux命令行实验(Smart ZYNQ SP版) (SL版不带此功能)

下面是PYNQ 部分的图文教程资料(已跑通,镜像在章节三, 还在整理测试中 2023年8月21日 )

- PYNQ 开发 章节一 开发移植环境的部署

- PYNQ 开发 章节二 Vivado 硬件工程搭建 (Smart Zynq SP & SL版)

- PYNQ 开发 章节三 PYNQ镜像构建 (Smart Zynq SP & SL版) (含可供测试的镜像链接)

备注 PYNQ部分仍然还在测试中,不一定完善,感兴趣的大家自行测试 2023年8月21日

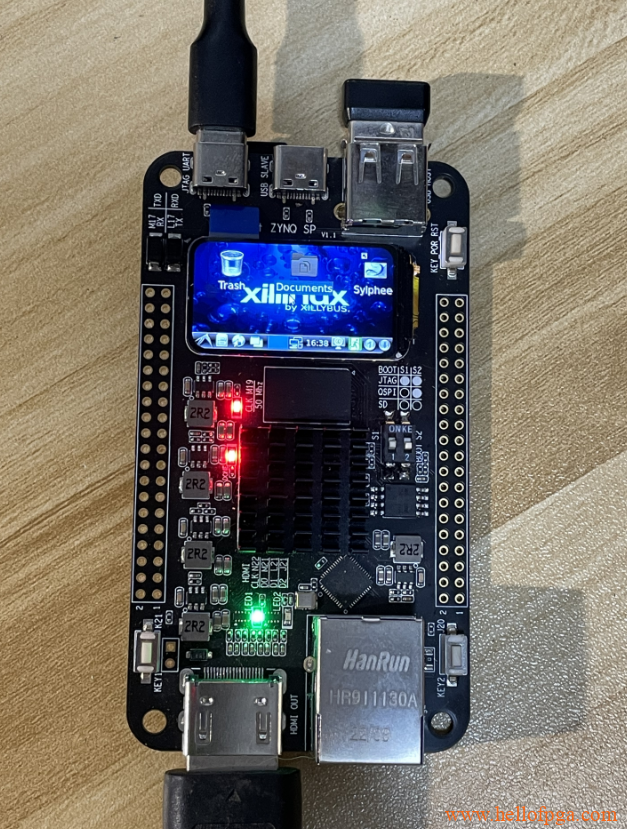

Xillinux 图形化操作系统重磅来袭(资料更新中)

- Xillinux 操作系统 资料整理

- Xillinux 章节一 TF卡准备工作之 镜像烧录

- Xillinux 章节二 TF卡准备工作之 demo bundle 的使用说明

- Xillinux 章节三 Xillinux 的启动验证

- Xillinux 章节四 调整 file system 的大小

- Xillinux 章节五 设置自定义Ethernet MAC 地址 (选看)

- Xillinux 章节六 使用SmartZynq SP上的板载SPI LCD屏幕

- Xillinux 章节七 EEPROM 存储实验

- Xillinux 章节八 GPIO的输入输出实验

- Xillinux 章节九 通过 ssh 远程登录 Xillinux

- Xillinux 章节十 Windows 通过 SCP 命令 远程传输文件给Xillinux 系统

- Xillinux 章节十一 Xillinux 使用CIFS 挂载 Windows共享文件夹

- Xillinux 章节十二 在Xillinux 系统上搭建 CIFS服务(samba),实现与Windows 文件共享

- Xillinux 章节十三 在Xillinux 系统中自动挂载(mount) TF卡分区

- Xillinux 章节十四 在 Windows 计算机上远程显示并操作Xillinux 桌面及应用

- Xillinux 章节十五 将普通耳机连接到 digital output pin 并播放音乐

- Xillinux 章节十六 使用 Smart Zynq 从 OV7670 摄像头模块进行实时取景和视频捕捉

- Xillinux 章节十六 (补充一)在 Smart Zynq主板上通过 I2C接口对 OV7670 相机传感器的寄存器进行配置

Xillinux 桌面操作系统演示图片

Xillinux 桌面操作系统演示图片

请教一下,ft2232的驱动是已经编译到bin中了吗?

ft2232 本身已经下载了固件, vivado 安装好后 会自带ft2232的驱动

想请教一下,smart的板子USB上电不一会儿就发热有些严重,请问该怎么办?

是主芯片吗?ZYNQ本身功耗不低的,如果是主芯片发热,但是功能正常的话,那属于正常情况(一般逻辑复杂的话主芯片上到50-60度都是可能的),板子出厂时候带的demo也会微微发热,把包裹里送的散热片一起贴上。

如果是其他芯片发热,或者主芯片异常发热(不能正常工作),那有可能是调试的时候某种情况造成板子烧坏了(通常这种情况会伴随各路电源短路的情况),如果你自己不能判断问题的话,就在购买的店铺联系我。或者寄回来我帮你检查

如果要用到usb口来实时传输数据,应该参考哪个例程呢?开发板上似乎并没有usb协议相关的芯片比如ft2232等,我如果要将8路数据从usb口发出到pc端,需要自行通过rtl编写数据包封包过程吗?

SP板上对应的 USB 口可以实现你的需求,但是数据需要从PS ARM端进行上传,不需要用RTL来编写USB驱动部分

请问大概需要如何操作呢?将数据存到ps端的DDR中后要如何通过usb口发出呢?例程中似乎没有如何使用usb口的介绍,只有一个如何将usb slave改为模拟U盘的例程

最近会做一个 USB SLAVE 和PC通讯的工程

谢谢

Smart ZYNQ (SP 版) OTG_USB 无法拉低

static unsigned int mio_base = 0;

#define MIO_BASE 0xE000A000

#define MIO_SIZE 0x1000

#define MIO_DIRM_1 (unsigned int *)(0x00000244 + mio_base)

#define MIO_OEN_1 (unsigned int *)(0x00000248 + mio_base)

#define MIO_DATA_1 (unsigned int *)(0x00000044 + mio_base)

static unsigned int clk_base = 0;

#define CLK_BASE 0xF8000000

#define CLK_SIZE 0x1000

#define APER_CLK_CTRL (unsigned int *)(0xF800012C – CLK_BASE + clk_base)

mio_base = (unsigned int)ioremap(MIO_BASE, MIO_SIZE);

clk_base = (unsigned int)ioremap(CLK_BASE, CLK_SIZE);

if(mio_base && clk_base){

*APER_CLK_CTRL |= (0x1U << 22);

*MIO_DIRM_1 |= (0x1U << 14);

printk("MIO_DIRM_1:%08x\r\n",*MIO_DIRM_1);

*MIO_OEN_1 |= (0x1U << 14);

printk("MIO_OEN_1:%08x\r\n",*MIO_OEN_1);

*MIO_DATA_1 &= ~(0x1U << 14);

printk("MIO_DATA_1:%08x\r\n",*MIO_DATA_1);

}

日志

MIO_DIRM_1:00004000

MIO_OEN_1:00004000

MIO_DATA_1:003f0000

看原理图被3.3V上拉,VIVADO MIO46 只有LVCMOS1.8V

在VIVADO MIO46脚 是可以设置成LVCMOS3.3的, 默认就是3.3 不知道您那边出现什么情况只能设置成1.8

另外我电路上 设备只能作为HOST 或者SLAVE ,而具体用哪种方式是由程序决定的。 硬件本身并不能作为OTG形式去识别电路是HOST 还是SLAVE

您可以使用我的测试工程试试,USB的SLAVE和HOST功能是否正常,再去查询程序的问题看看

USB SLVAE 的功能正常,但是USB3320 ULPI PHY需要在重启时复位一次,偶尔软重启后,会认不到PHY。

如果你系统自动复位的方式无法工作,也可以按照我刚说的 把MIO46这个信号当作普通IO进行手动复位操作

通过示波器看,测量OTG_USB始终是高电平。软重启后一直维持高电平。

你说的是哪个信号线 ,USB部分电路并没有 OTG_USB这个信号线,你是说USB 复位信号?

USB_RESET这个信号 在VIVADO 中设置的,默认是自动完成复位操作的

如果你那边工程一直有问题, 你也可以在VIVADO里 取消 USB_RESET 信号, 手动添加MIO46,然后在你的程序中 对MIO46进行手动复位(MI46 对应硬件上的 USB_RESET)

您能分享一下 ft2232 固件或编程指南吗?我已经安装了 vivado,但 windows 无法识别任何 jtag 或 uart 设备

你的 ft2232是自制的 还是说我板子上自带的?

win下没有识别到jtag 有两种可能

1 ft2232设备被识别成其他的eda下载器了(之前有安装了其他的EDA下载器驱动)这个从设备管理器里就能看出,可以重新安装vivado 目录中的驱动即可

2 ft2232 内部的固件是有问题的, 固件被覆盖了,或者自制的电路没有载入正确的固件。

You have connected the VCC3V3 power supply to pins 37 and 38 of the U12 connector. It’s stupid. It was necessary to connect VCCIO_ADJ.

我用苹果充电器连接USBslave口供电,USBhost口接无线网卡,在xillinux系统里识别不到网卡,接在串口usb供电就可以正常识别

USB HOST 和SLAVE 口是公用 数据线的, 如果你的 苹果充电器里 会占用 USB DP DN 数据线 那就会影响 USB host功能