包含Smart Artix 的原理图,注意事项,以及后续更新的转接板的原理图等一些资料

首先感谢各位的关注和支持,有任何问题可以直接在本站留言

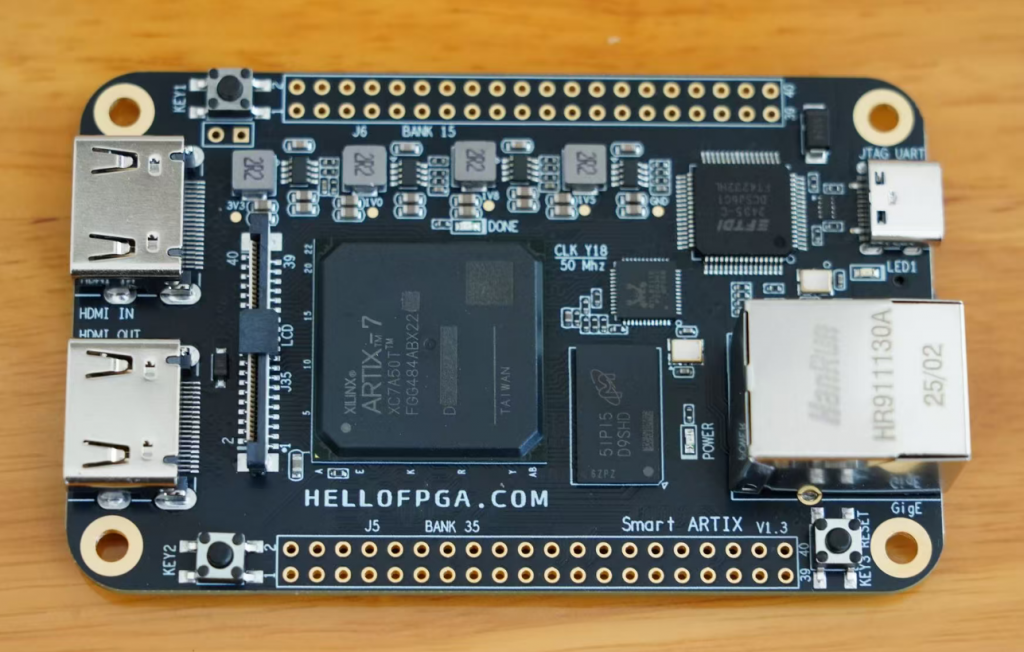

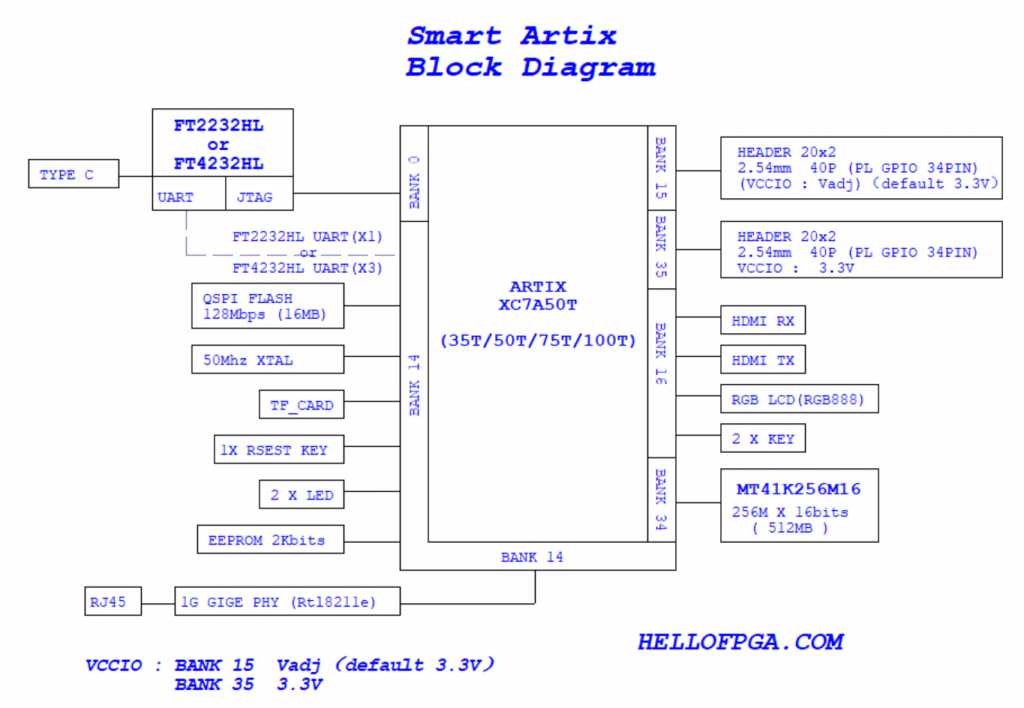

Smart Artix 主板资源

- 主芯片:ARTIX XC7A50T-2FGG484I

- 主板层数:8层(沉金工艺)

- DDR内存 : 256M x 16bit (512MB)

- FLASH : 128Mbits (16MB)(可用于程序固化和启动)

- EEPROM: 24C02 2Kbits

- TF插槽:microSD 插槽 (TF卡插槽)

- 时钟 :50M有源晶振

- 网络: 一路千兆以太网RTL8211E

- HDMI: 两路HDMI 接口(IO模拟) 一路负责发送,一路负责接收

- JTAG: 板子集成了 xilinx jtag 下载器部分功能(板载)

- 串口: 带1路 USB-UART (和JTAG 共用 TYPE C 接口)

- 备注:UART首批使用的芯片是FT4232HL,会映射出3路串口,3路串口均连接了FPGA的IO端

- 按键: 3个按键 (其中一个按键 是并RC的,可以充当系统RESET用)

- LED: 2个可编程LED(PL端 )+1个Done 指示LED + 1个电源指示LED

- LCD:带一路40PIN的RGB LCD 接口(40P FPC),接口线序兼容本站及正点原子的RGB屏

- 逻辑IO: 总共引出68个FPGA_IO,所有引出的管脚均以差分线方式两两引出(差分线内等长,同一边排针的BANK组内也全部等长)

- 引出的GPIO中 其中一边的bank电压单独可改(通过更换一个SOT23-5的 LDO来实现)另一边固定3.3V

- 电源:主板可以通过TYPE C口(JTAG或 USB SLAVE)进行供电,或者用转接板通过排针给主板的VCC脚供上5V电源

原理图尺寸图等:

备注:Smart Artix主板 第一版就是V1.3版,因为排针部分和Smart ZYNQ V1.3版兼容,所以为了方便理解Smart Artix主板也从V1.3版开始编号。

V1.3版主板原理图如下 (V1.3版即使初始版本,不存在V1.1 V1.2)(最新更新 2025年11月20日)

尺寸图

板子上所有功能IC 的数据手册:

注意事项

- 关于TYPE C的JTAG芯片, 由于FT芯片价格波动厉害,所以主板在设计上兼容了FT4232HL和FT2232HL两个JTAG芯片型号,如果主板是贴FT4232HL,那么接电脑上会出现3个串口(都是可以使用的),如果主板上贴的是FT2232HL,那么串口只有一路(首批主板贴的是FT4232HL)

- 板子上的TYPE C接口可为板子进行供电,板子排针上的VCC口也可以外接5V 为板子进行供电,USB和排针外接供电互不冲突(USB有二极管作电源防倒流保护),另外备注:部分台式机前面的USB口线损较大,如用台式机的USB供电出现不稳定的情况,请尝试连接台式机背后的USB口。

- 排针上的VCC口可作为电源输入,也可作为电源输出。作为输入时:可外接5V电源(即通过转接板,或者底板为板子供电,如用杜邦线供电效果会差一些)。作为输出时:(没有外接5V电源,仅通过USB供电时)可以输出4.5-4.7V的电压(即主板为转接板供电)。

- 板子上的RST KEY在电路上接了RC上电复位,所以这个按键可以充当复位按键使用,当然如果你的工程里不使用外部复位信号,那这个按键也是可以作为可编程按键使用的。

- 关于BANK15的电压, BANK 15电压可以通过更换背面SOT23-5封装的LDO芯片(板子上丝印有标注)来实现电压的调整(出厂默认是3.3V)

- 板子上的网络部分电路已经开启了PHY 芯片内部的 RX DLY 和 TX DLY功能,因此在 VIVADO 工程中不需要再额外添加 DLY 部分。如果使用 Xilinx 官方的网络 MAC IP,请确保将 DLY 功能关闭(或将IP的 90 度时钟偏移输入信号,直接连接到正常的网络时钟,而无需进行偏移处理)

随板预下载的演示程序介绍 (QSPI FLASH启动)(26年1月更新)

- HDMI输出720p的 测试彩色条纹

- UART(含3路)在按下rst按键瞬间输出”HELLOFPGA.COM”,之后进入回环模式(接收到什么数据,回复相同数据,波特率115200)

- LED灯在上电后以流水灯的方式 来回点亮 (一旦按下KEY1 KEY2 任意按键,则流水灯停止,程序切换到对应按键方向的灯亮起) (LED灯功能与DDR3读写功能同样绑定,如果任何一盏LED灯亮起就代表DDR3测试通过)

- DDR3读写测试,工程在运行的时候将对整个DDR区域进行读写检验, 如果读写校验都通过,则上一条对应的LED灯功能正常工作, 如果DDR3校验出问题,则两盏LED全都熄灭。

- 网络进入UDP回环模式(可用网络助手进行调试,开发板IP为192.168.1.10,本地PC IP需设置成192.168.1.102,端口1234进行调试, 详细测试方法请看UDP相关DEMO),备注:预下载的demo不带 ICMP功能,所以无法进行ping操作

已整理的一些图文例程

备注 本站所有的资料都是基于VIVADO2018.3版本的,如果不熟悉开发过程,版本尽量保持一致

- 基于Smart Artix 的FPGA程序固化流程(固化至QSPI FLASH) (工程基于实验一)

- 基于Smart Artix 的FPGA实验一 用FPGA资源点亮一个LED(完整图文)

- 基于Smart Artix 的FPGA实验二 用FPGA资源设计流水灯

- 基于Smart Artix 的FPGA实验三 基于FPGA的按键功能演示(IO输入功能)

- 基于Smart Artix 的FPGA实验四 Vivado自带的仿真功能演示

- 基于Smart Artix 的FPGA实验五 FPGA 硬件调试 ILA功能的演示

- 基于Smart Artix 的FPGA实验六 FPGA的 VIO在线调试功能测试

- 基于Smart Artix 的FPGA实验七 FPGA资源的PWM演示

- 基于Smart Artix 的FPGA实验八 FPGA片内资源MMCM/PLL 时钟模块的测试

- 基于Smart Artix 的FPGA实验九 FPGA片内资源 BLOCK RAM IP核的使用

- 基于Smart Artix 的FPGA实验十 调用片内XADC资源来读取 ADC对应管脚的电平电压

- 基于Smart Artix 的FPGA实验十一 基于双路高速ADC模块的信号采集实验

- 基于Smart Artix 的FPGA实验十二 基于FPGA逻辑资源的HDMI TX 功能演示

- 基于Smart Artix 的FPGA实验十三 基于FPGA逻辑资源的HDMI 发送与接收的回环功能演示

- 基于Smart Artix 的FPGA实验十四 基于FPGA的RGB888屏幕调试 (5INCH 800X480屏)

- 基于Smart Artix 的FPGA实验十五 基于FPGA的 UART串口通讯实验

- 基于Smart Artix 的FPGA实验十六 基于FPGA的DDR3内存读写实验

- 基于Smart Artix 的FPGA实验十七 基于FPGA的千兆以太网UDP环回实验

(新内容正在整理中)