ZYNQ7010 和诸多FPGA一样,从JTAG 下载的二进制文件,断电默认丢失的,为了让程序断电仍然可以工作,本文将演示,如何把代码固化到 EBAZ4205的NAND FLASH 中

(备注 一般调试不需要固化程序,当程序需要永久保存时候 可以考虑将程序进行固化)

1)ZYNQ启动流程

1.首先了解ZYNQ的启动过程, ZYNQ的启动过程以 ARM核为主, 上电后 硬件先读取ARM核PS端的IO 以确定 系统从NAND ,QSPI ,SD Card还是 JTAG 启动系统。 (EBAZ4205板子默认硬件是从NAND FLASH 驱动的)

2.ARM的普通FPGA(非ZYNQ)固化是直接将BIT文件通过QSPI写入FLASH就行的,但是对于 ZYNQ 来说,必须要有 PS 端的配合才能固化程序

2) 实际操作演示

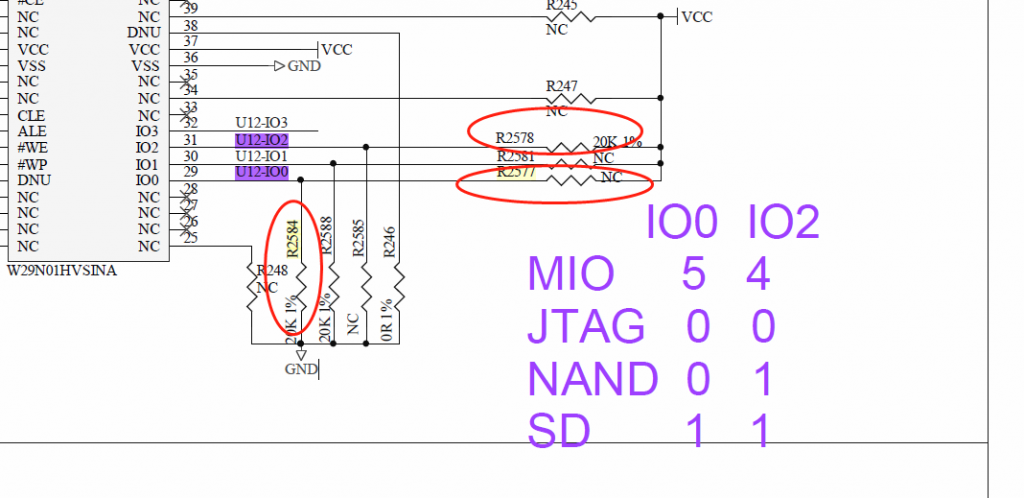

具体的启动方式如下图所示, 系统上电瞬间检测IO0 和IO2两个管脚,用来区分不同的上电方式, 这里我们只要关注 NAND JTAG SD 三种启动方式就好。

操作,让系统从JTAG 方式启动,以进入调试模式

EBAZ4205 原先硬件默认从NAND方式进行启动, 要想对NAND进行程序的固化,我们需要让板子临时从JTAG调试模式进行启动(临时性的) ,只需要在上电瞬间让IO2保持低电平状态即可。

如下图所示, 可选择 镊子 在板子上电前让 R2585 保持短路状态, 之后再上电,让系统从JTAG模式启动

操作请务必小心 别伤到走线和电路

3) 软件部分配置

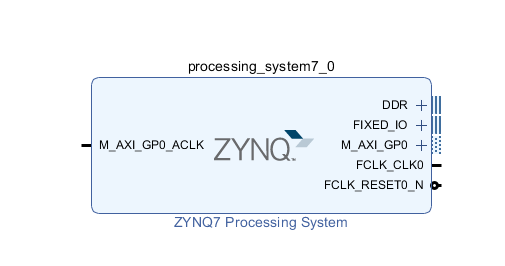

1.创建工程–>create block design–>”+”–>检索zynq7 processing system 并添加

2.添加ZYNQ 7处理器模块

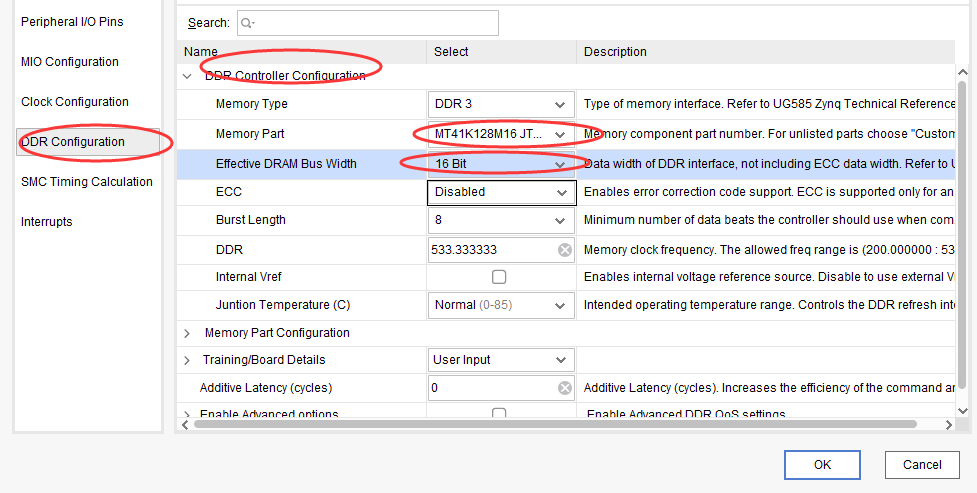

依次在弹窗里找到DDR Configuration→DDR Controller Configuration→DDR3,在Memory Part下拉菜单中根据自己板子上的DDR来选择相应的DDR3,本实验所用到型号:MT41K128M16JT 125,数据位宽选择16bit 最后点击“OK”,如下图所示。

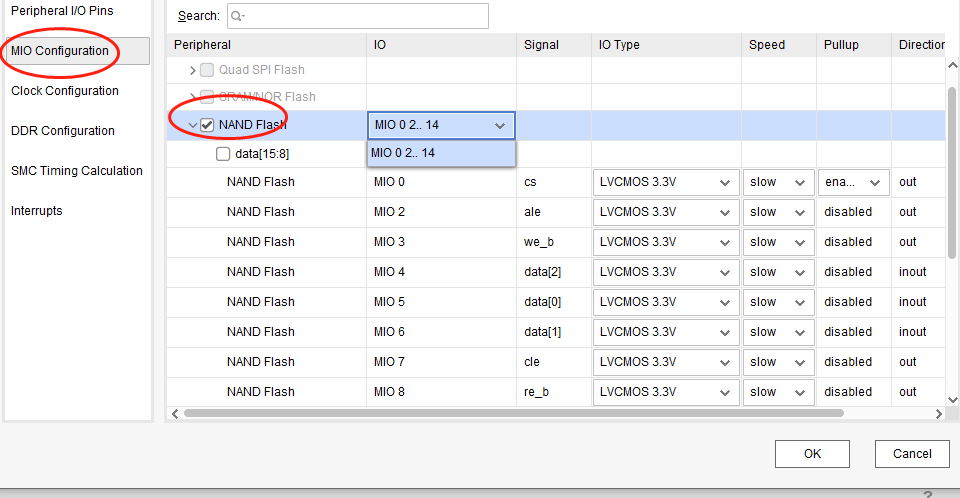

3.为系统添加Nand flash 功能

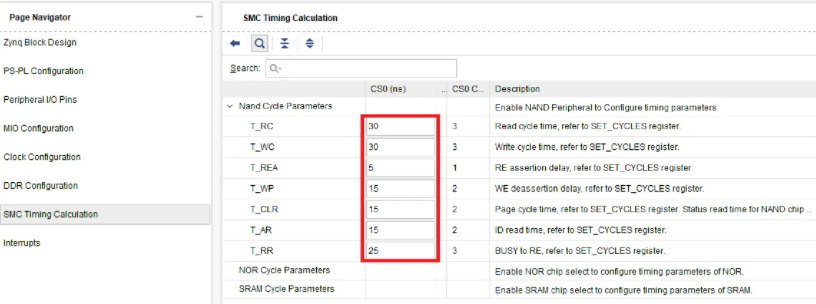

4.对nand 参数进行设置 ( SMC )

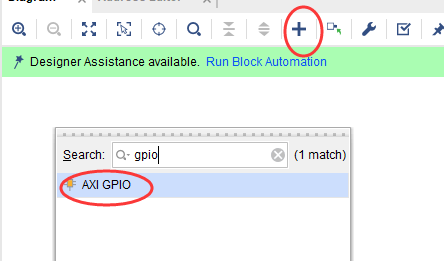

5.添加GPIO 以用来演示功能

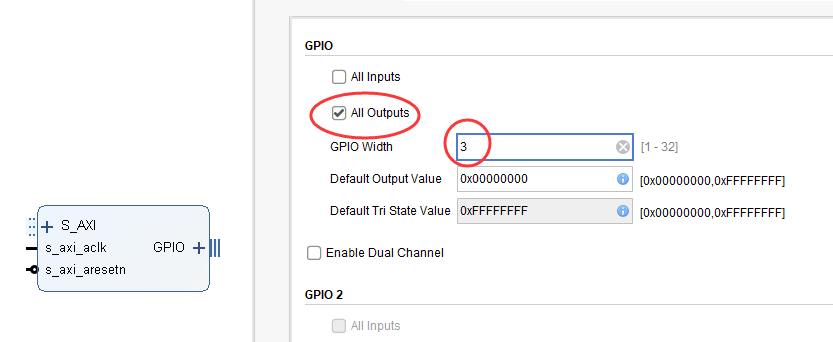

6)在GPIO的设置栏里将输入输出属性改成全部输出ALL Outputs ,因为我们板子上只有3个LED灯,所以将GPIO Width位宽设置成3位,点击OK

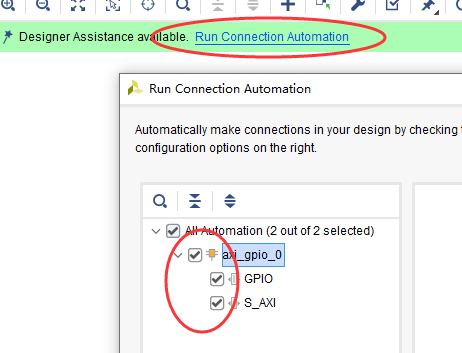

7)点击 上方的Run Connection Automation ,并将GPIO 和S_AXI前面的勾都选中,如下图所示 点击OK

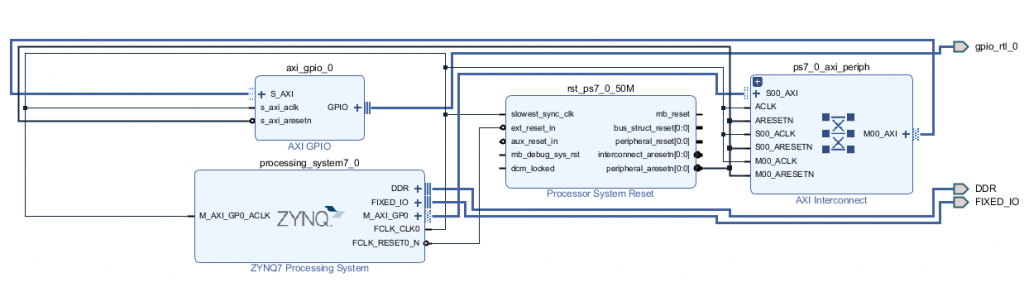

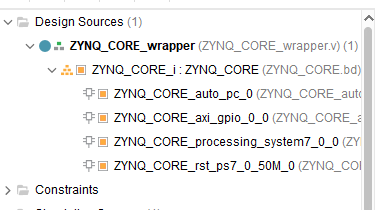

8)软件将自动帮我们完整所有必要的连线,以及添加必要的模块

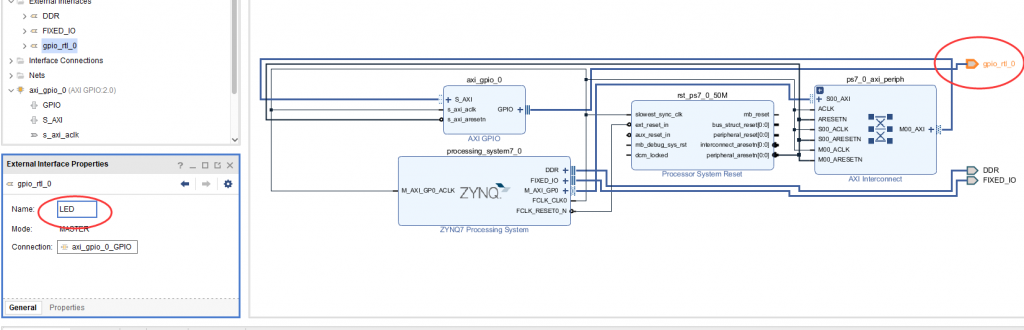

9)在框图中双击GPIO输出的管脚,并重新命名为LED,方便后面软件编程

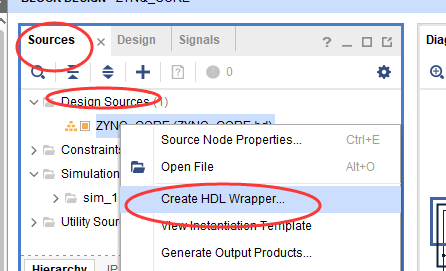

10)source→Design Source ,右键我们创建的BLOCK工程,点击create HDL wrapper如下图所示。

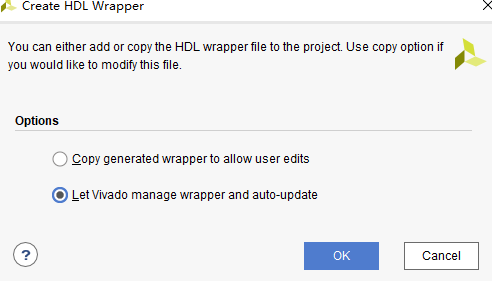

在弹出的对黄框里保持默认

软件自动为我们生成HDL文件

11)添加管脚约束

set_property PACKAGE_PIN H18 [get_ports {LED_tri_o[2]}]

set_property PACKAGE_PIN E17 [get_ports {LED_tri_o[1]}]

set_property PACKAGE_PIN K19 [get_ports {LED_tri_o[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED_tri_o[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED_tri_o[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED_tri_o[0]}]

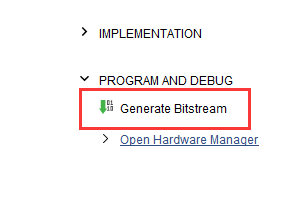

12)生成bit文件

按下绿色箭头对工程进行编译

按下Generate Bitstream 完成综合以及生成bit文件

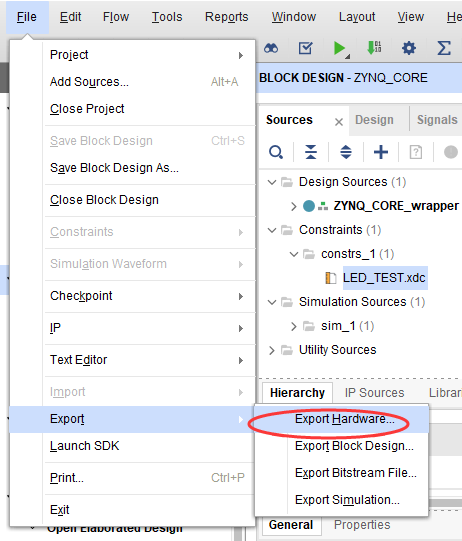

4 SDK部分配置

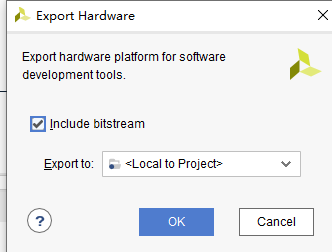

1)File→Export→Export hardware…,在弹出的对话框中勾选“include bitstream”,点击“OK”确认,如下图所示。

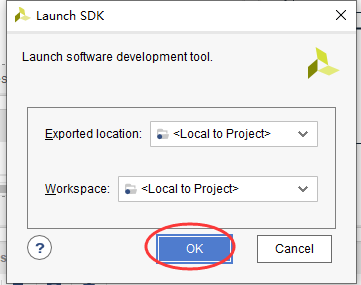

2)File→Lauch SDK,在弹出的对话框中,保存默认,点击“OK”,如下图所示。

系统将自动打开SDK开发环境

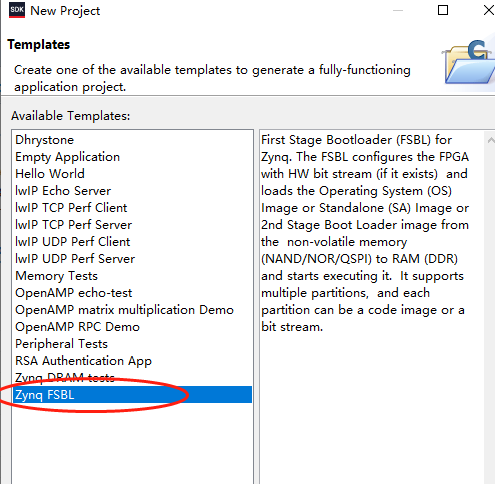

3)在SDK中新建如下,然后设置工程名fsbl,点next选择FSBL模板

4)再按照工程六创建LED的演示工程,这样就有两个工程了, fsbl工程用于初始化ddr等。保存编译产生两个elf即 led工程的.elf 和fsbl.elf

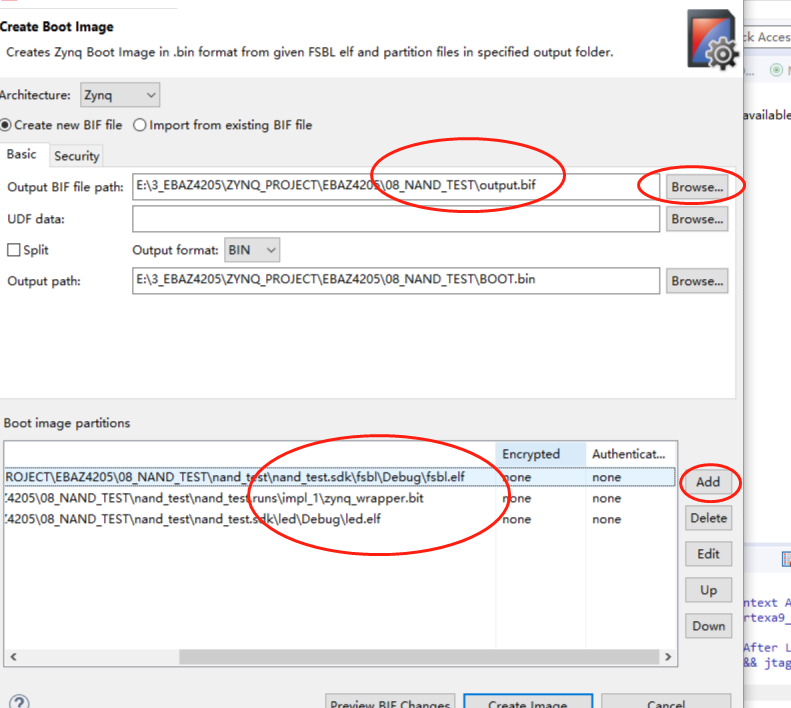

5)制作BOOT.bin用于固化到NAND。BOOT.bin由fsbl.elf文件 vivado生成的fpga 的bit文件 app工程的elf文件(这里为led工程的elf)三个文件组成。

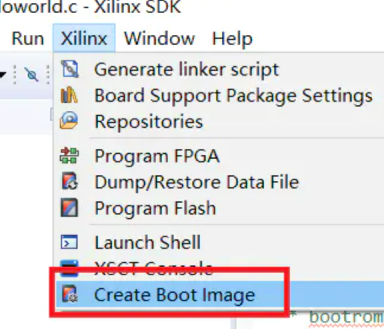

点xilinx –>create boot image

6.在界面里分别设置 boot.bin的输出路径,以及生成boot.bin需要的三个文件的路径

首先设置输出路径

再分别导入三个文件 ,要注意三个文件类型不同,fsql 属于bootload ,另外两个是datefile

都完成后点击,create image 生成 镜像文件

7,生成完boot.bin后,下一步将boot.bin 下载到nand flash 中

(注意, 下载前先断电, 然后让ZYNQ 进入 JTAG模式, 文章一开始有提到)

按上图操作 导入 boot 文件,和fsbl.elf文件后 点击PROGRAM 开始下载

下载成功后,重新上电, 正常的话扩展板的LED 会交替闪烁,说明板子的FPGA 已经正常初始化完整,flash 下载成功

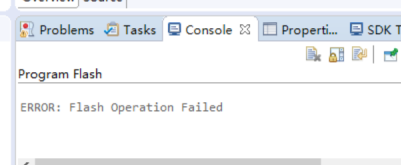

如果下载过程中出现下图所示,说明系统上电时没有正常进入JTAG 调试模式,请进入JTAG模式后再尝试

完整工程如下:

楼主记录很详细啊~ 入门必备

请问下楼主使用的是什么版本的vivado呢?

jtag显示成功擦除代码但是无法写入,找不到解决方法

我一直用的 2018.3版本, 检查下你的拨码是否设置成JTAG模式