PS端与PL端在硬件上是相互独立的,之前可以通过EMIO 和 AXI GPIO等方式 让ZYNQ PS 端的GPIO 口映射到PL端上,但是仅仅只能控制GPIO。 本文介绍一种新的方法,通过让PS端访问PL端寄存器的方式,来让ARM 和FPGA实现简单的数据交互(小数据量)

- 实验内容适用于市面上功能正常的EBAZ4205的板子

- 本次实验需要连接本站点的EBAZ4205转接板

- 本次实验没有用到PL端晶振

- 本文在 vivado2018.3版本上演示

一、Vivado工程创建

工程创建的过程可以参考实验一中的内容,这里不详细描述了。基于EBAZ4205的PS实验一 GPIO之用EMIO方式点亮LED(完整图文)(芯片型号选XC7Z010CLG400-1)

二、创建一个带AXI 接口的IP

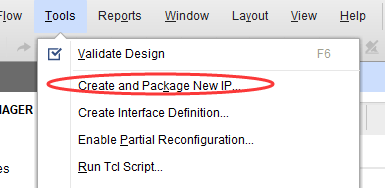

- 创建并封装一个带AXI 接口的IP 具体过程如下 ,TOOLS->Create and Package New IP

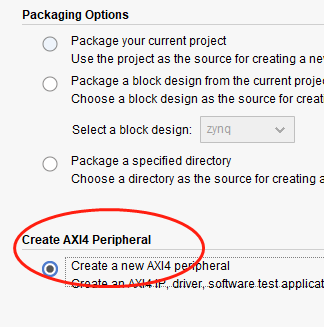

2.选择封装带AXI4总线的

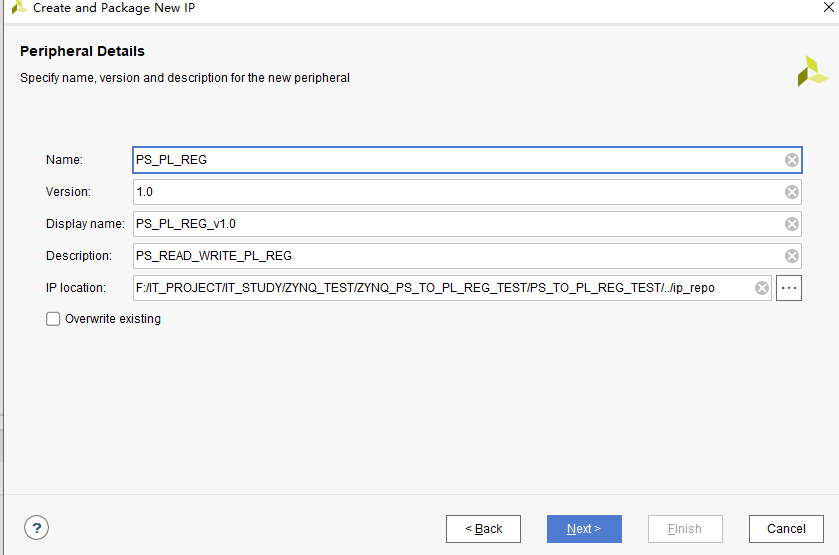

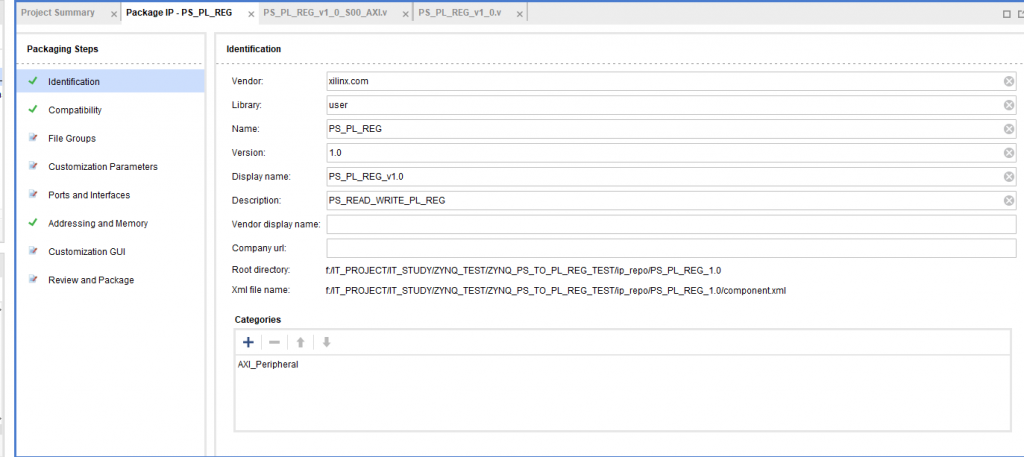

3、next,填写名称等信息,注意IP保存路径。这里给IP取名 PS_PL_REG 即 PS和PL的REG互相访问

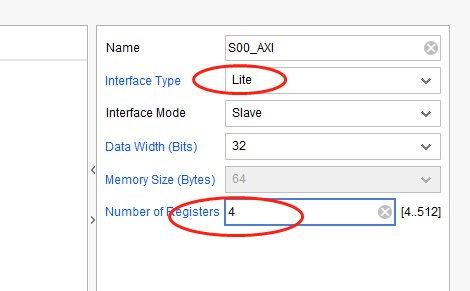

4、next,选择总线相关信息,这里AXI的 协议选择 LITE 轻型, 然后number of registers 根据需求选择,4即代表有四个32bit的寄存器 最小选择是4个

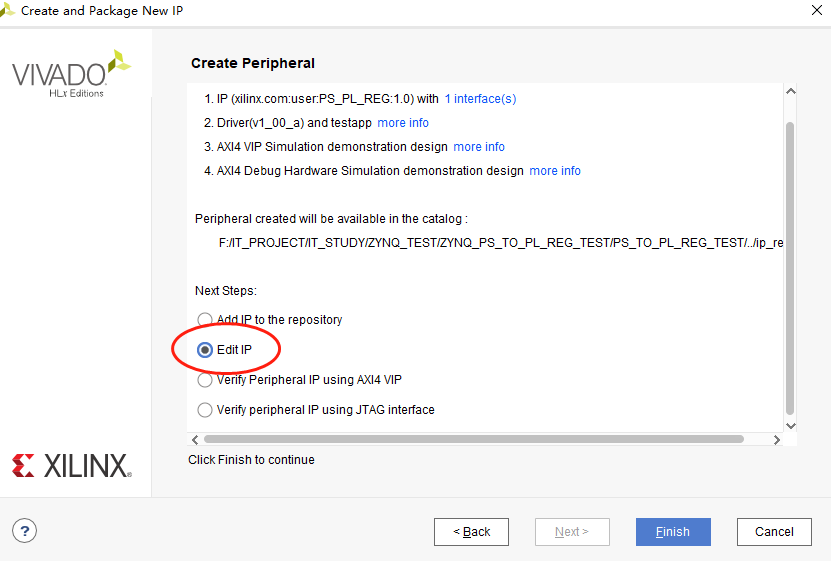

5.选择 下一步 EDIT IP 并点FINISH完成(这里一定要选择“Edit IP”,否则,软件只是生成了框架文件,而不会创建一个关于IP 核的工程)

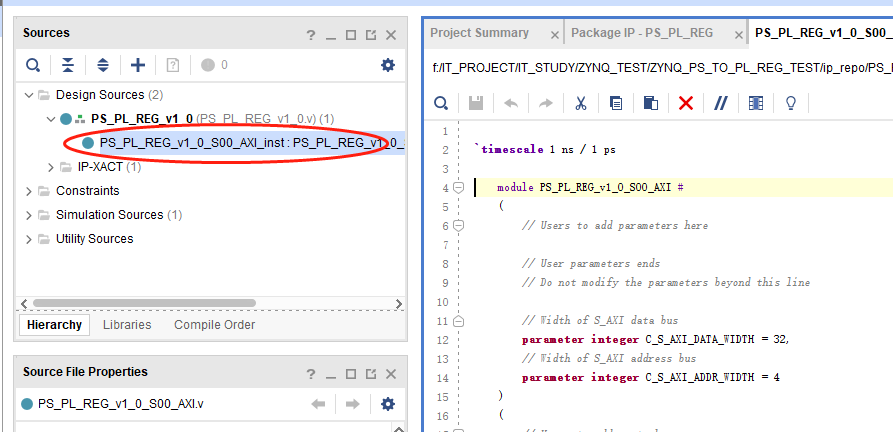

6.之后系统会自动生成一个该IP的工程。 这里我们双击打开系统默认生成的IP代码

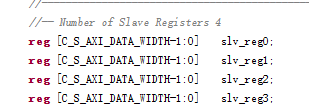

7.研究代码,可以看到 我们设置IP的时候 PL端的4个用于PS访问的寄存器分别是 slv_reg0,slv_reg1,slv_reg2,svl_reg3 ,这4个寄存器 通过AXI 接口,可供ARM PS端进行读和写的操作。

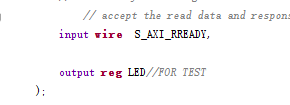

8.为了让交互的过程更为直观,我们在原有的IP代码中添加一个LED指示灯用来观察交互的结果

output reg LED;

并在代码中增加以下代码用来将灯和数据进行对应

always@(posedge S_AXI_ACLK)begin

if(slv_reg0==32'd0)LED<=0;

else if(slv_reg0<=32'd1)LED<=1;

end代码解释 ,当slv_reg0等于32位的0时 LED 熄灭, 当slv_reg0等于32‘d1时,即十进制1时,LED点亮(slv_reg0后面可由ARM端的程序直接读写)

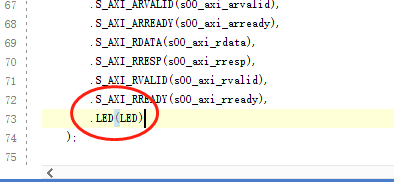

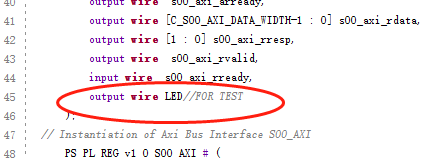

9.对系统生成的IP的上层模块,也相应的增加LED 接口,并与内部的模块相连接

10.编辑完后,保存修改,接下来是打包 修改完的IP(封装之前,先编译综合看看代码是否有报报错),回到Package IP页面设置IP,如下所示输入相关信息,也可以不修改

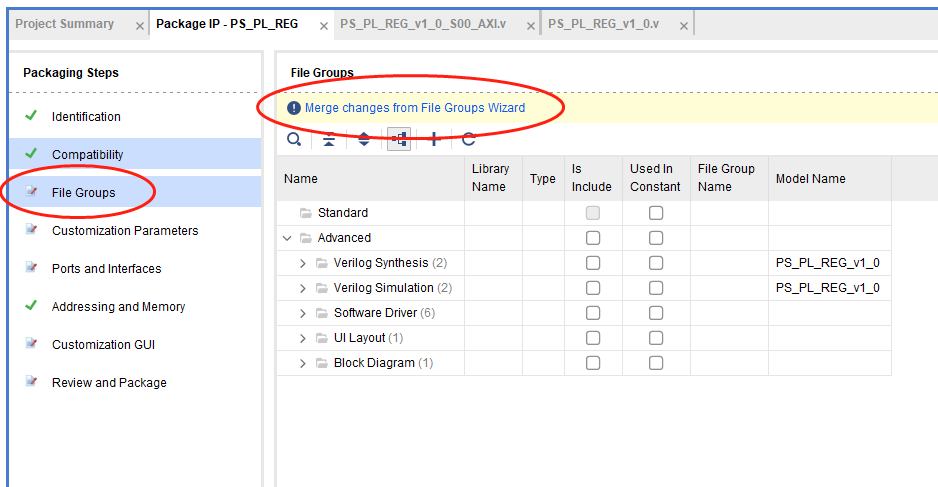

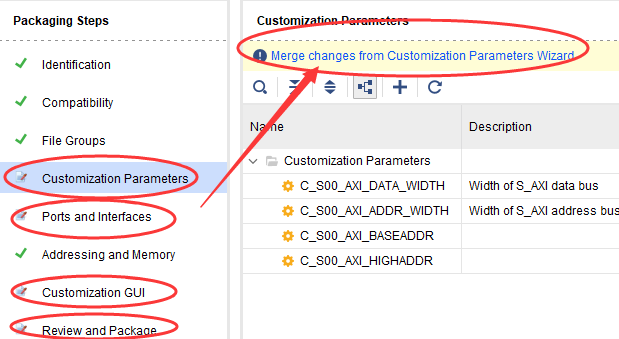

在file Groups项中点击Merge changs from File Groups Wizard

根据上面的操作,也将软件界面中没有打勾的 选项全部都merge了

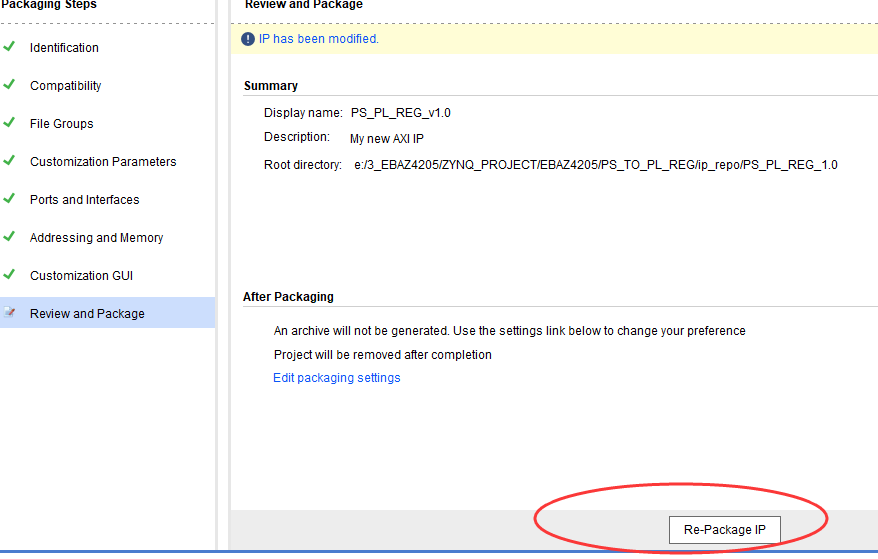

当除了最后一项,所有的选项都勾上更新后, 在最后一栏里点重新打包封装IP,完成IP的打包

IP打包后,修改IP的工程会被系统自动关闭

三、在vivado工程中增加ZYNQ模块

1.增加ZYNQ 模块

1)在Block Design 中 增加ZYNQ模块,并且在设置界面 将DDR选项设置成 MT41K128M16JT 位宽选择16bit

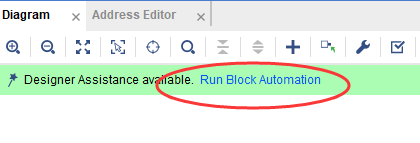

2)选择 Run Block Automation 完成端口自动布线

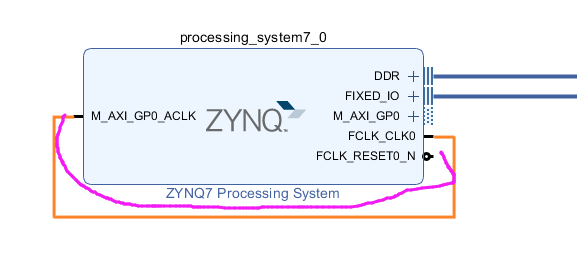

3)手动连接 FCLK_CLK0到 M_AXI_GP0_ACLK

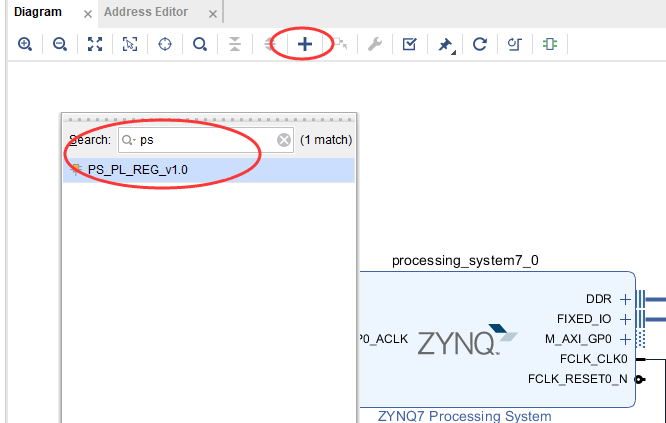

4)在block design 中添加我们刚才创建的PS_TO_PL_REG IP模块

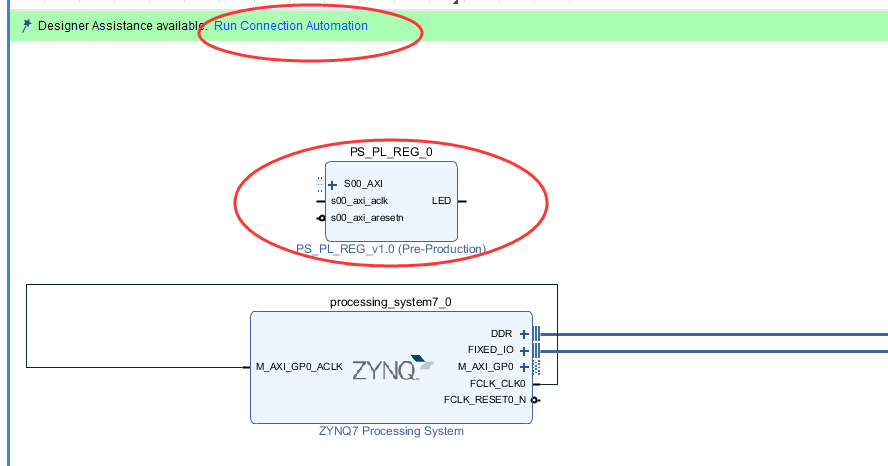

5) 如下图所示 我们添加的PS_PL_REG模块已经添加到设计中,再次点选run connection automation尝试自动连线

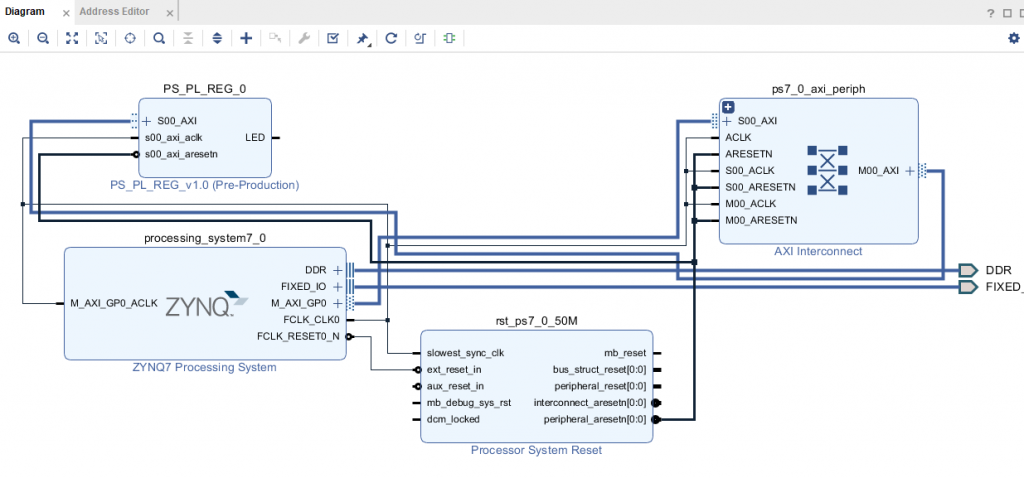

如下图所示,系统为我们自动添加需要增加的模块,并自动连接好了各个模块

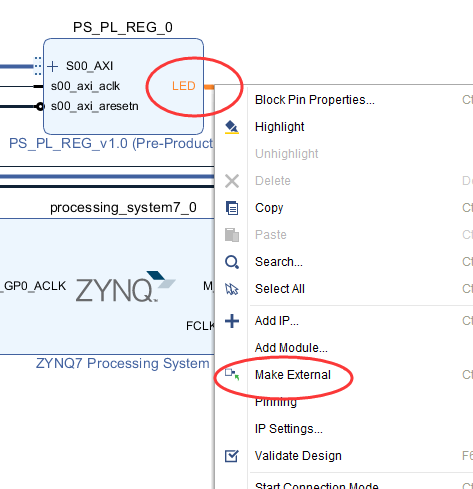

6) 因为我们的演示 是需要通过LED 来观察结果的,所以这里右键LED 将LED窗口印出来

这样我们的整个硬件系统就算布局完成了。

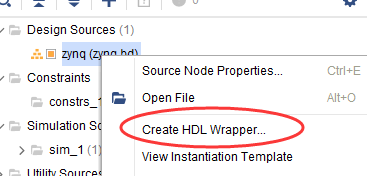

7) 在design Sources中 右键我们刚刚设计的ZYNQ模块,然后点选 Create HDL Wrapper

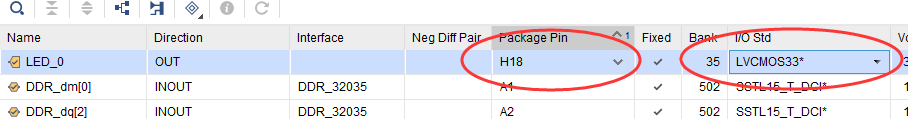

8)编译 , 为LED 分配管脚 H18是 扩展板上的LED 管脚

9)为LED 分配管脚

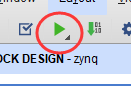

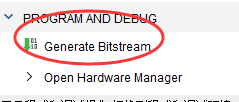

10)综合并生成 bit文件

三、PS部分工程创建

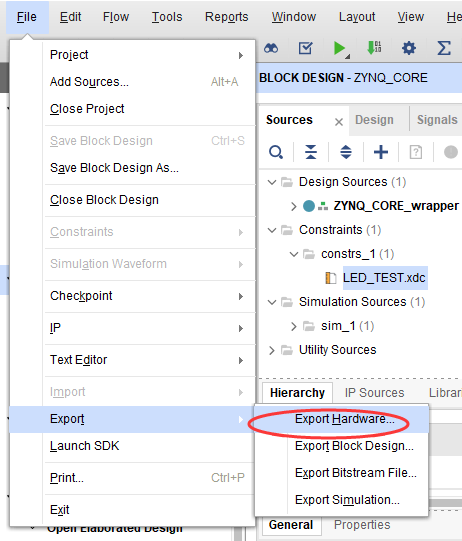

1)File→Export→Export hardware…,在弹出的对话框中勾选“include bitstream”,点击“OK”确认,如下图所示。

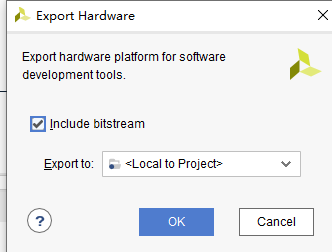

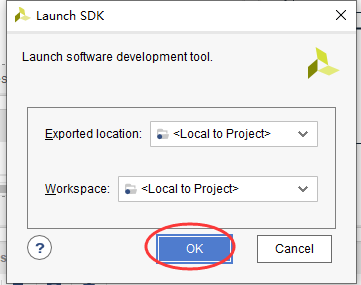

2)File→Lauch SDK,在弹出的对话框中,保存默认,点击“OK”,如下图所示。

系统将自动打开SDK开发环境

系统将自动打开SDK开发环境

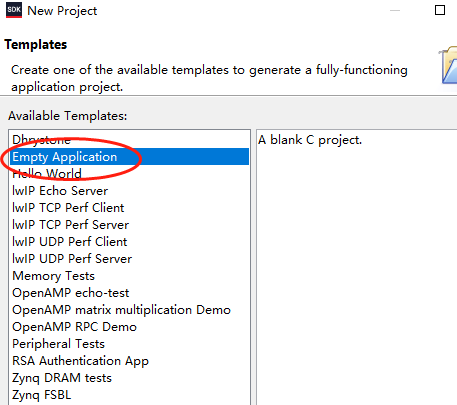

3)再创建一个LED 工程,负责LED 指示灯的闪烁

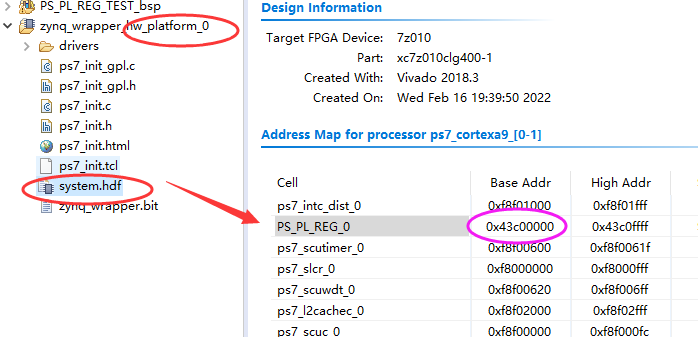

a. 创建一个新的空工程,可以取名叫PS_PL_REG_TEST

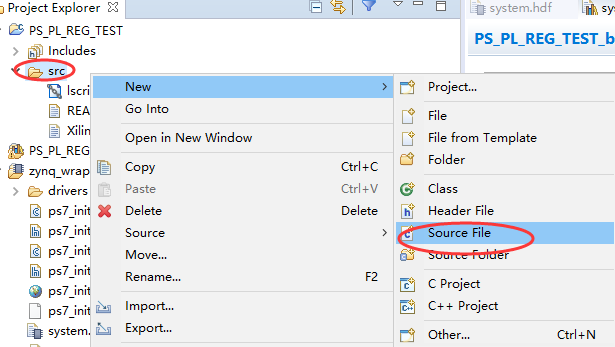

b.右键工程的SRC目录,然后新建一个SOURCE FILE

c.取名 main.c

四、PS端代码编写

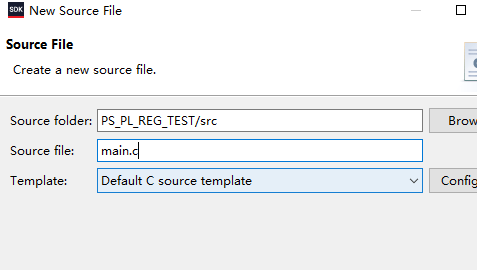

1.点开platform中的 system.hdf 这里所有的资源都会显示在这里, 找到我们之前创建的PS_PL_REG ,可以看到 这个外设的基地址是 0X43C00000 ,后面我们会用到这个地址

2.在main .c中添加如下代码

#include "xparameters.h"

#include "xil_io.h"

#define LED_BASE_ADDR 0x43c00000

int main()

{

volatile int Delay;

while(1)

{

Xil_Out32(LED_BASE_ADDR, 1);

for (Delay = 0; Delay < 10000000; Delay++);

Xil_Out32(LED_BASE_ADDR, 0);

for (Delay = 0; Delay < 10000000; Delay++);

}

return 0;

}

五、下载与验证

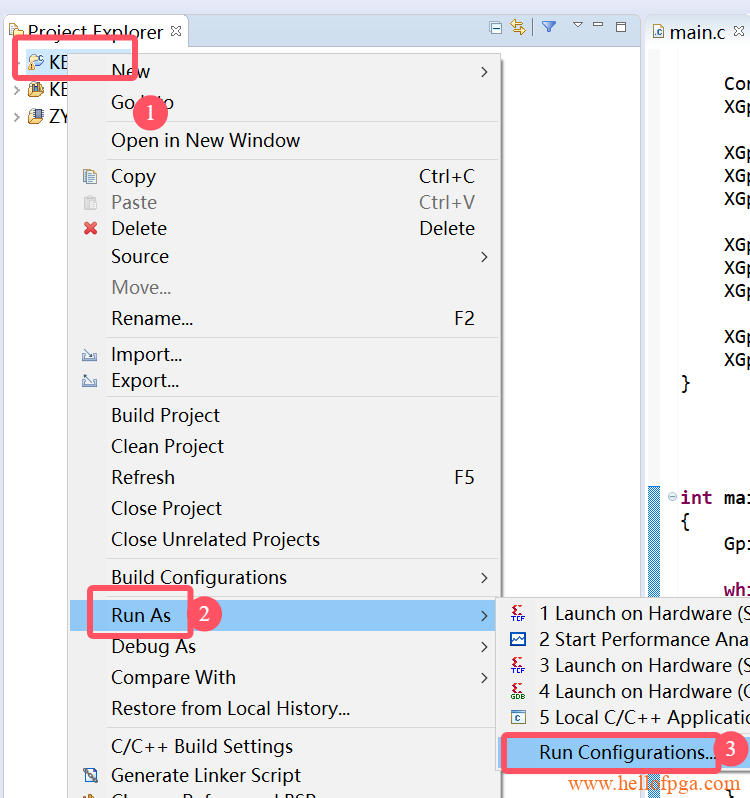

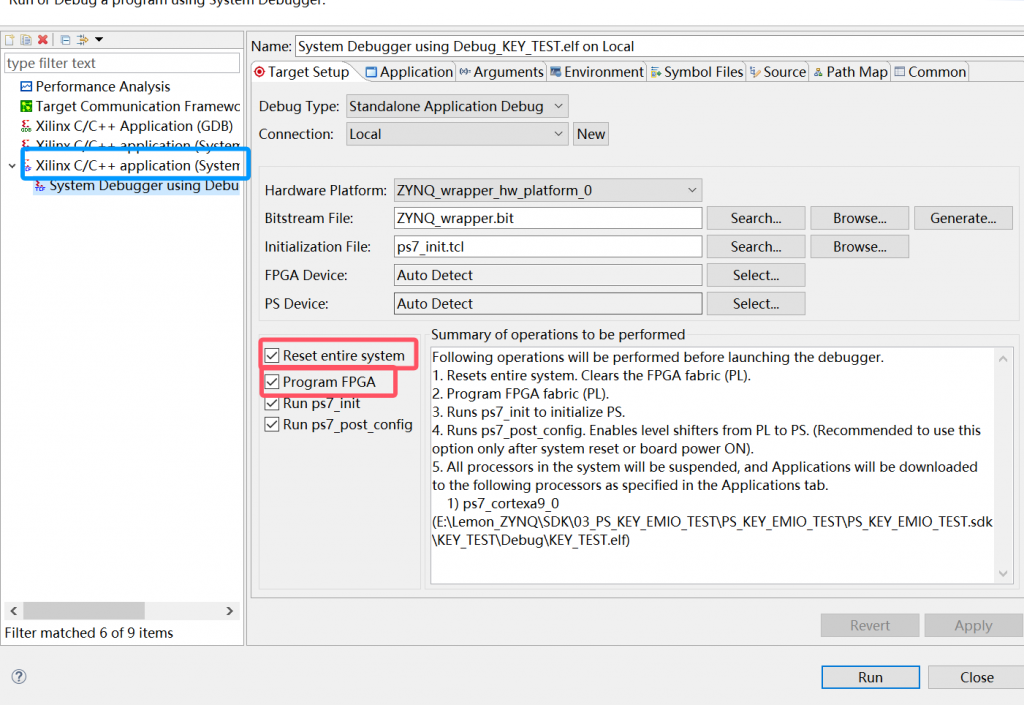

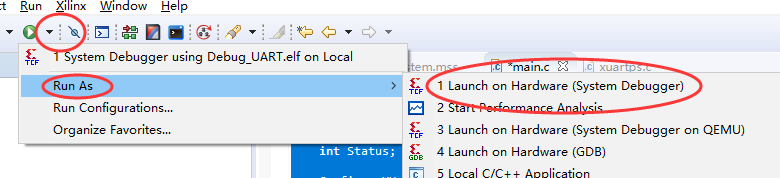

1)新创建的工程最好先对Run as 进行配置:右键工程,并点选Run As -> Run Configurations

2) 在弹出的窗口中对Reset entire system 和 Program FPGA两个选项进行勾选操作,这样就不会出现下载程序debug的时候概率性不工作的问题了。(这样操作后系统会自动对FPGA进行配置,不需要按之前工程手动对FPGA进行编程了)

PS如果没有出现下图对话框,可以直接双击左侧的applicationo (System Debugger)。

3)设置好之后,选择Run As -> Launch on Hardware (System Debugger) 进行调试。

可以看到板子上的LED1灯在闪烁

六、代码解读

#define LED_BASE_ADDR 0x43c00000,这里的0X43C00000就是我们之前看到的 模块地址

Xil_Out32(LED_BASE_ADDR, 1); 相当于向上面的模块地址写入1

Xil_Out32(LED_BASE_ADDR,0) ; 相当于向模块的基地址写入0

因为我们在PL端创建的模块中的4个寄存器,只有寄存器0对应了LED ,所以我们只要向基地址写入信息就可以控制LED 指示灯了。

如果要控制寄存器1,寄存器2 ,寄存器3 只需要在基地址的基础上+4就可以了 (+4是因为数据都是32bit的)

另外我们也可以反向用PS 去读取PL端的寄存器值,具体过程不展开描述了, 实际PS访问 可以通过指令Xil_In32(LED_BASE_ADDR); (LED_BASE_ADDR 为我们定义的基地址 )来进行读取。

通过上述方式 我们成功的实现了 PS和PL 通过寄存器方式的交互,这种方式相对比较简单 容易入手,当然交互的方式还有很多,后面 有时间再继续整理。

七、简单介绍读取部分(本部分新增加,没有提供工程,大家自行尝试)

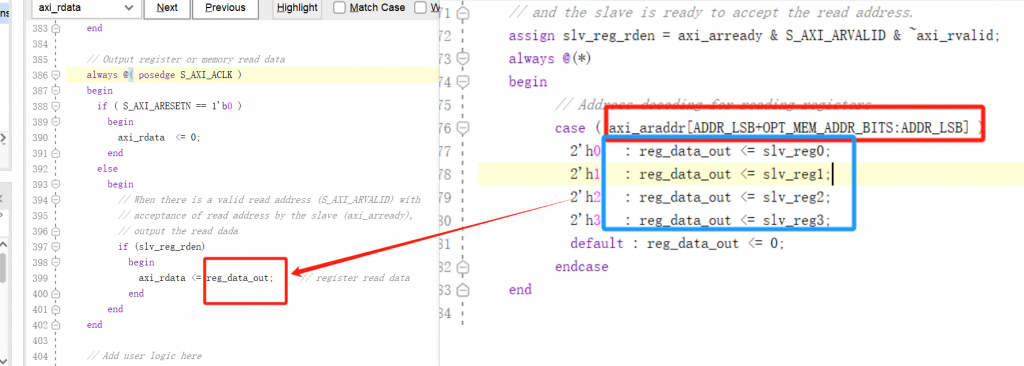

回到系统自动生成的 IP 模块中(如下图所示),axi_rdata 是我们从 PL 侧读取数据时返回给 PS 的通道。而另一个 always 模块则负责根据当前访问的地址,选择返回哪个寄存器的数据。

由于我们的示例(demo)中共定义了 4 路 32 位寄存器,因此在地址匹配部分有 4 个 case 分支来对应不同的寄存器地址。

需要注意的是,这个 IP 是由 Xilinx 工具自动生成的 AXI 外设模板,其原始用途是演示 PS 通过 AXI 接口对寄存器进行读写操作的回环功能(loopback demo)。因此,在读操作中返回的数据正是之前通过写操作写入的值(例如 slv_reg0 等)。

要实现我们自己的数据写入,我们只需要将地址切换的4个case 的输入端改成自己的寄存器或wire 即可(即将slv_reg0等寄存器换成自己的数据)。为了方便演示,这里我们直接给定固定的32位数字(32’d1,32’d3,32’d5,32’d7)。实际大家可以把这个常数改成自己输入的reg 或者wire。

assign slv_reg_rden = axi_arready & S_AXI_ARVALID & ~axi_rvalid;

always @(*)

begin

// Address decoding for reading registers

case ( axi_araddr[ADDR_LSB+OPT_MEM_ADDR_BITS:ADDR_LSB] )

2'h0 : reg_data_out <= 32'd1;

2'h1 : reg_data_out <= 32'd3;

2'h2 : reg_data_out <= 32'd5;

2'h3 : reg_data_out <= 32'd7;

default : reg_data_out <= 0;

endcase

end

之后按上文介绍的流程重新 打包IP,并且在主工程中重新更新IP,以及对工程重新进行编译综合和Export。(Export之后 SDK也会提示更新,点更新即可)

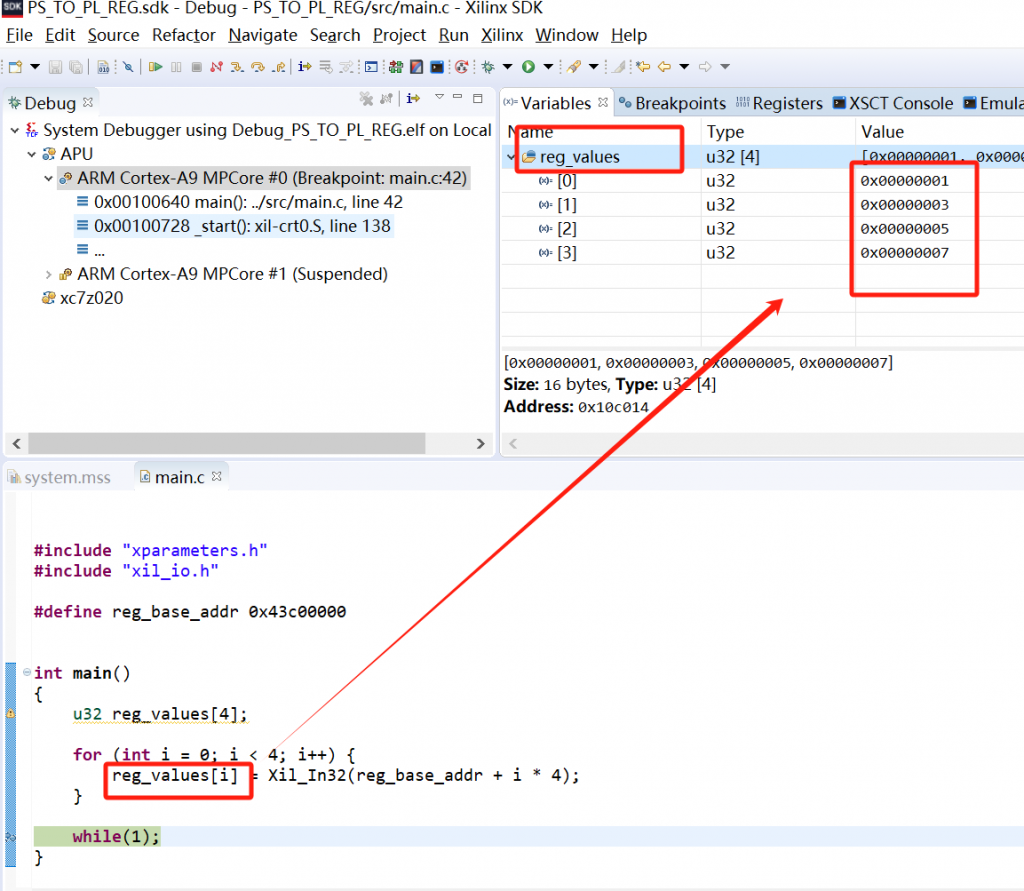

在SDK 下的代码也比较简单,用一个for 循环分别用Xil_In32去读这4个寄存器的地址

#include "xparameters.h"

#include "xil_io.h"

#define reg_base_addr 0x43c00000

int main()

{

u32 reg_values[4];

for (int i = 0; i < 4; i++) {

reg_values[i] = Xil_In32(reg_base_addr + i * 4);

}

while(1);

}

接下来,点击工具栏上的小甲虫(Debug)按钮,将程序下载到开发板并开始调试。在 while(1) 处设置一个断点,运行程序后,当程序停在断点处时,可以观察到 reg_values[i] 中读取到的数据正是我们在 PL 端预设的 4 个常数(1、3、5、7),这说明寄存器读取功能已经成功实现。

(本部分新增加,没有提供工程,大家自行尝试)

本章节的工程:

- 本文的完整工程下载: 09_PS_TO_PL_REG

- VIVADO的版本:2018.3

- 工程适用主板: EBAZ4205主板+转接板

有个问题请教您:

1、上面这个工程只是用PS部分跑了个裸程序,并不是基于linux系统的工程吧?

2、vivado里面新建的PS工程,与网上说的搭建PS部分的linux开发环境,区别在哪里?

是的 ,上面这个工程是用来实现 PS部分和PL部分,数据共享用的,程序确实是裸奔的,没有跑任何操作系统 我对linux 这块不是特别熟, 不过据我所知 创建linux开发环境 好像需要在 linux下进行kernal的编译, 当然 如果用现成的 linux 镜像直接跑应该也是没问题的, vivado创建的PS 工程比较底层, linux 的工程比较上层,也就是你在zynq上跑linux ,剩下的程序就都相当于是在linux下开发驱动和APP了

感谢您分享知识

always@(posedge S_AXI_ACLK)begin

if(slv_reg0==32’d0)LED<=0;

else if(slv_reg0<=32'd1)LED<=1;

end

是不是拼写错误?错误在IP中如何调试发现?

我这样看好像没有问题, 编译的时候错误提示是什么

您好, 感谢分享。 请教一下外设的基地址这里的0x43C00000,可以自行修改成其他地址么?如果可以在哪里修改? 谢谢!

在Block Design 里的 Address Editor 里设置